【導(dǎo)讀】負(fù)載電容(load capacitance)常用的標(biāo)準(zhǔn)值有12.5 pF,16 pF,20 pF,30pF,負(fù)載電容與石英諧振器一起決定振蕩器的工作頻率,通過(guò)調(diào)整負(fù)載電容,一般可以將振蕩器的工作頻率調(diào)到標(biāo)稱值。

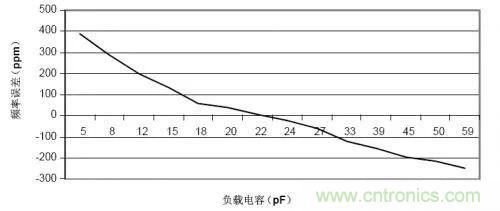

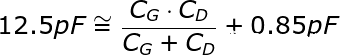

負(fù)載電容和諧振頻率之間的關(guān)系不是線性的,負(fù)載電容變小時(shí),頻率偏差量變大;負(fù)載電容提高時(shí),頻率偏差減小。下圖是一個(gè)

晶體的負(fù)載電容和頻率的誤差的關(guān)系圖。

圖1、晶振誤差— 負(fù)載電容(22 pF 負(fù)載電容)

負(fù)載電容的定義

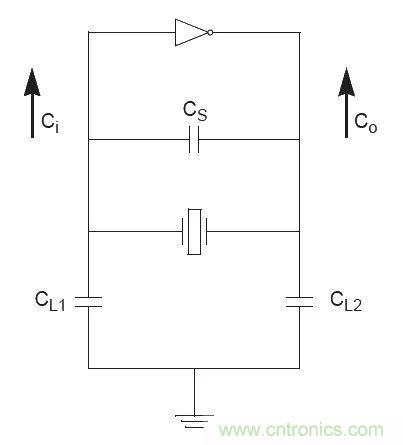

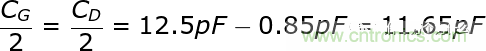

從石英晶體插腳兩端向振蕩電路方向看進(jìn)去的全部有效電容為該振蕩電路加給石英晶體的負(fù)載電容。石英晶體的負(fù)載電容的定義如下式:

圖1中標(biāo)示出了CG,CD,CS的的組成部分。

圖1、晶體振蕩電路的概要組成

CG指的是晶體振蕩電路輸入管腳到gnd的總電容(比如 USB PHY的USB_XI信號(hào)到地)。容值為以下三個(gè)部分的和。

● USB_XI管腳到gnd的寄生電容, Ci

● 晶體-震蕩電路XI的PCB走線到到gnd的寄生電容,CPCBXI

● 電路上另外增加的并聯(lián)到gnd“負(fù)載電容”, CL1

CD指的是晶體振蕩電路輸入管腳到gnd的總電容(比如 USB PHY的USB_XO信號(hào)到地)。容值為以下三個(gè)部分的和。

● USB_XO管腳到gnd的寄生電容, Co

● 晶體-震蕩電路XO的PCB走線到到gnd的寄生電容,CPCBXO

● 電路上另外增加的并聯(lián)到gnd“負(fù)載電容”, CL2

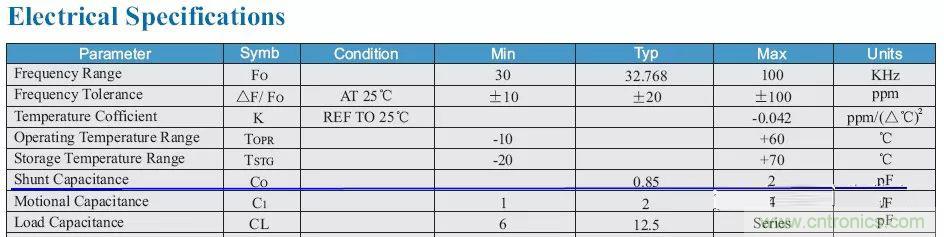

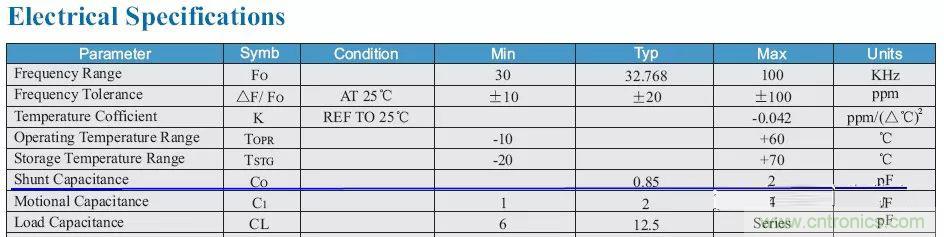

CS指的晶體兩個(gè)管腳之間的寄生電容(shunt capacitance),在晶體的規(guī)格書上可以找到具體值,一般0.2pF~8pF不等。如圖二是某32.768KHz的電氣參數(shù),其寄生電容典型值是0.85pF(在表格中采用的是Co)。

圖2、某晶體的電氣參數(shù)

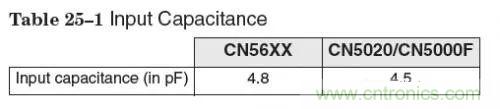

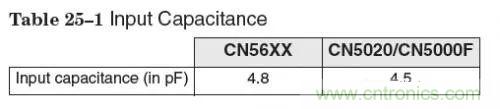

Ci以及Co的取值,一般可以在芯片手冊(cè)上查詢到。比如圖三是某芯片的XI/XO的寄生電容值。

圖3、某芯片的輸入電容

CL1/CL2的計(jì)算過(guò)程

一般我們會(huì)說(shuō),計(jì)算晶體振蕩電路的負(fù)載電容,事實(shí)上是根據(jù)晶體規(guī)格書上標(biāo)稱的負(fù)載電容,計(jì)算出實(shí)際需要在晶體兩端安裝的電容CL1以及CL2的值。

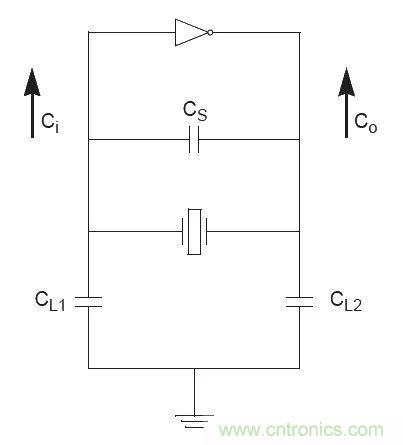

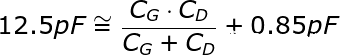

假設(shè)我們需要計(jì)算的電路參數(shù)如下所述。芯片管腳的輸入電容如圖三CN56XX所示,Ci=4.8pF;所需要采用的晶體規(guī)格如圖二所示,負(fù)載電容CL=12.5pF,晶體的寄生電容CS=0.85pF。

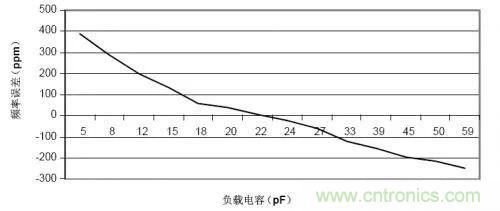

我們可以得到下式:

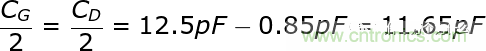

為了保持晶體的負(fù)載平衡,在實(shí)際應(yīng)用中,一般要求CG=CD,所以進(jìn)一步可以得到下式:

根據(jù)CG的組成部分,可以得到:

CG=Ci+CPCBXI+CL1=23.3pF

晶體布線時(shí)都會(huì)要求晶體盡量靠近振蕩電路,所以CPCBXI一般比較小,取0.2pF;Ci=4.8pF。所以最終的計(jì)算結(jié)果如下:(CL2的計(jì)算過(guò)程類似)

CL1=CL2=18.3pF≈18pF

例外情況

現(xiàn)在有很多芯片內(nèi)部已經(jīng)增加了補(bǔ)償電容(internal capacitance),所以在設(shè)計(jì)的時(shí)候,只需要選按照芯片datasheet推薦的負(fù)載電容值的選擇晶體即可,不需要額外再加電容。但是因?yàn)閷?shí)際設(shè)計(jì)的寄生電路的不確定性,最好還是預(yù)留CL1/CL2的位置。

以上的計(jì)算都是基于CG=CD的前提,的確有一些意外情況,比如cypress的帶RTC的nvsram的時(shí)鐘晶體要求兩邊不對(duì)稱,但是幸運(yùn)的是,cypress給出了詳細(xì)的計(jì)算過(guò)程以及選型參考。

推薦閱讀: