基于FPGA 設(shè)計(jì)數(shù)字日歷可以實(shí)現(xiàn)以軟件方式設(shè)計(jì)硬件的目的,無(wú)需購(gòu)買專用數(shù)字芯片,從而克服了傳統(tǒng)利用多片數(shù)字集成電路設(shè)計(jì)數(shù)字日歷存在焊接麻煩、調(diào)試繁瑣、成本較高等問題。而且,基于FPGA 的數(shù)字日歷與傳統(tǒng)系統(tǒng)相比,在設(shè)計(jì)靈活、開發(fā)速度、降低成本、計(jì)時(shí)精度、功能實(shí)現(xiàn)上都得到大幅度提升,能夠更好地滿足人們?nèi)粘I畹男枰?br />

本文介紹如何利用VHDL 硬件描述語(yǔ)言設(shè)計(jì)一個(gè)具有年、月、日、星期、時(shí)、分、秒計(jì)時(shí)顯示功能,時(shí)間調(diào)整功能和整點(diǎn)報(bào)時(shí)功能的數(shù)字日歷。在Quartus Ⅱ開發(fā)環(huán)境下,采用自頂向下的設(shè)計(jì)方法,建立各個(gè)基本模塊,再構(gòu)建成一個(gè)完整的基于FPGA 設(shè)計(jì)的數(shù)字日歷的頂層模塊,然后對(duì)其進(jìn)行編譯、仿真、引腳鎖定,最終下載到可編程邏輯器件上進(jìn)行結(jié)果驗(yàn)證。

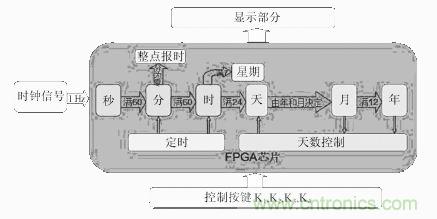

1 數(shù)字日歷整體設(shè)計(jì)方案

基于FPGA 的數(shù)字日歷設(shè)計(jì)分為硬件設(shè)計(jì)和軟件設(shè)計(jì)兩大部分。其原理框圖如圖1所示。整個(gè)數(shù)字日歷由六個(gè)部分組成:顯示控制部分,時(shí)分秒部分,年月日部分,定時(shí)與整點(diǎn)報(bào)時(shí)部分,星期部分,調(diào)整控制部分。秒、分、時(shí)分別由兩個(gè)60進(jìn)制的計(jì)數(shù)器和一個(gè)24進(jìn)制的計(jì)數(shù)器組成。當(dāng)個(gè)計(jì)數(shù)器達(dá)到進(jìn)位的條件時(shí)向下一計(jì)數(shù)器進(jìn)位。同樣日、月、年也是由不同的計(jì)數(shù)器組成,當(dāng)達(dá)到所需進(jìn)位的條件時(shí)向下一計(jì)數(shù)器進(jìn)位,各計(jì)數(shù)器在進(jìn)位的同時(shí)分別把各自的結(jié)果輸出給顯示部分進(jìn)行實(shí)時(shí)顯示。

首先由外部振蕩器產(chǎn)生穩(wěn)定的高頻脈沖信號(hào),作為數(shù)字日歷的時(shí)間基準(zhǔn),然后經(jīng)過分頻器輸出標(biāo)準(zhǔn)秒脈沖,輸入到FPGA的CLOCK端,實(shí)現(xiàn)計(jì)數(shù)。當(dāng)秒計(jì)數(shù)器滿60后向分計(jì)數(shù)器進(jìn)位,分計(jì)數(shù)器滿60后向小時(shí)計(jì)數(shù)器進(jìn)位,小時(shí)計(jì)數(shù)器按照“24進(jìn)1”規(guī)律計(jì)數(shù)。計(jì)滿后各計(jì)數(shù)器清零,重新計(jì)數(shù)。日部分由于日有28天、29天、30天、31天4種情況,故日由年和月共同判斷其天數(shù),日計(jì)滿后向月進(jìn)位,月滿后向年進(jìn)位。計(jì)數(shù)器的輸出分別經(jīng)譯碼器送數(shù)碼管顯示。計(jì)時(shí)出現(xiàn)誤差時(shí),可以用校時(shí)電路校時(shí)、校分、校秒和校年、校月、校日。

設(shè)計(jì)中用到了6 個(gè)按鍵K1,K2,K3,K4,ZHENG,NAO。其中K1用于切換顯示,剛開始時(shí)顯示日期,按兩次K1顯示星期+時(shí)間,再按兩次K1顯示定時(shí)時(shí)間,再按兩次重新顯示日期,以此循環(huán)。K2、K3和K4配合進(jìn)行調(diào)節(jié):開始正常顯示不進(jìn)行調(diào)節(jié);當(dāng)按兩下K2 鍵切換到對(duì)分鐘進(jìn)行調(diào)節(jié),此時(shí)每按兩下K3 鍵分鐘加1;再按兩下K2 鍵切換到對(duì)小時(shí)進(jìn)行調(diào)節(jié),此時(shí)每按兩下K3 鍵小時(shí)加1;依照分鐘→小時(shí)→星期→天→月→年→定時(shí)→正常→分鐘的次序循環(huán)調(diào)節(jié),每按兩下K2 鍵切換到調(diào)節(jié)相應(yīng)顯示,此時(shí)每按下K3鍵兩次,對(duì)應(yīng)顯示加1;當(dāng)切換到定時(shí)調(diào)節(jié)時(shí),每按兩下K3鍵,定時(shí)的分鐘加1,此時(shí)按兩下K4 鍵,切換到定時(shí)小時(shí)調(diào)節(jié),每按兩下K3 鍵,定時(shí)的小時(shí)加1。按鍵ZHENG和NAO為整點(diǎn)報(bào)時(shí)和定時(shí)鬧鐘的使能端(低電平有效)。

3 軟件設(shè)計(jì)

軟件設(shè)計(jì)分為秒分時(shí)、年月日、按鍵調(diào)整、控制顯示、鬧鐘等幾大模塊。設(shè)計(jì)好各子模塊,然后在原理圖編輯窗口創(chuàng)建頂層原理圖文件shuzirili.bdf,將各子模塊按照邏輯關(guān)系連接起來得到數(shù)字日歷電路核心部分的原理圖。下面對(duì)各子模塊設(shè)計(jì)及仿真進(jìn)行介紹。

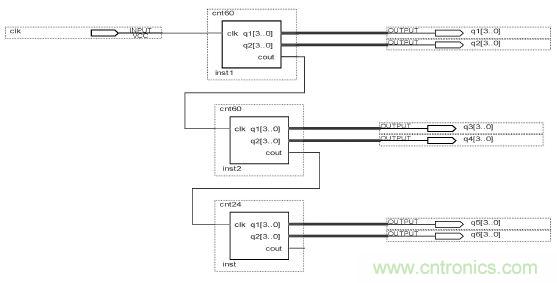

3.1 時(shí)分秒模塊

分和秒都是60進(jìn)制的計(jì)數(shù)器,小時(shí)則是24進(jìn)制的計(jì)數(shù)器,先對(duì)各個(gè)子模塊進(jìn)行設(shè)計(jì)編譯,驗(yàn)證無(wú)誤后再將其組織到一起。外部時(shí)鐘信號(hào)通過秒模塊的clk 輸入,產(chǎn)生的進(jìn)位信號(hào)輸送到分模塊的clk,分模塊產(chǎn)生的進(jìn)位信號(hào)輸送到小時(shí)模塊的clk,構(gòu)成時(shí)分秒模塊。其結(jié)構(gòu)圖如圖2所示。

3.2 星期模塊

星期模塊為七進(jìn)制計(jì)數(shù)器。其計(jì)數(shù)時(shí)鐘信號(hào)來自于調(diào)時(shí)電路產(chǎn)生的星期進(jìn)位脈沖信號(hào),計(jì)數(shù)至6 瞬間,計(jì)星期模塊返回0 重新開始計(jì)數(shù)。

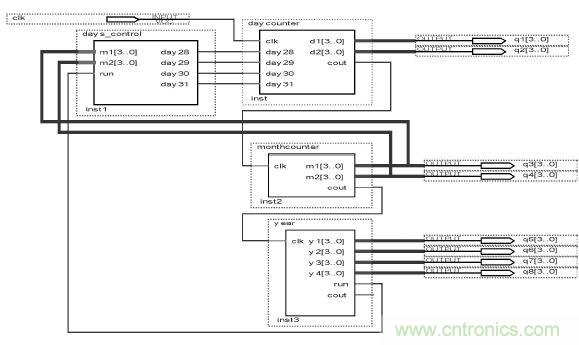

3.3 年月日模塊

年月日模塊有daycounter 模塊、days-control 模塊、monthcounter模塊、yearcounter模塊組成,具有大小月判斷和閏年判斷功能,其結(jié)構(gòu)圖如圖3所示。

定時(shí)模塊通過按鍵K4來切換調(diào)節(jié)定時(shí)的分鐘和小時(shí),調(diào)整功能由調(diào)時(shí)模塊的按鍵K3來完成,每按兩下K3對(duì)應(yīng)的顯示加1。

3.5 調(diào)時(shí)模塊

調(diào)時(shí)模塊設(shè)計(jì)思想是:通過把整個(gè)設(shè)計(jì)中的上一個(gè)模塊(比如:分的上一個(gè)模塊是秒;年的上一個(gè)模塊是月,等等)的進(jìn)位輸出接到本模塊的輸入in,out接到下一個(gè)模塊的時(shí)鐘輸入。正常狀態(tài)下sout=fin,fout=hin,hout=din,dout=min,mout=yin ,win=hout;當(dāng)每按下兩次K2鍵,產(chǎn)生一個(gè)上升沿分別對(duì)fin,hin,win,din,min,yin,dingshi調(diào)節(jié),調(diào)節(jié)信號(hào)由K3 給出。其中定義一個(gè)信號(hào)w,計(jì)數(shù)到7 返0,對(duì)應(yīng)正常狀態(tài),fin,hin,win,din,min,yin,dingshi 7個(gè)狀態(tài)。

當(dāng)K2 每來一個(gè)上升沿時(shí),分別對(duì)分,時(shí),星期,天,月,年以及定時(shí)調(diào)整,調(diào)整信號(hào)由K3 給出,經(jīng)仿真調(diào)時(shí)模塊結(jié)果與系統(tǒng)設(shè)計(jì)要求符合。

3.6 控制模塊

控制模塊通過K1按鍵進(jìn)行切換顯示調(diào)整,起初顯示年月日,按下2次K1顯示時(shí)間,再按下2次顯示定時(shí)時(shí)間。

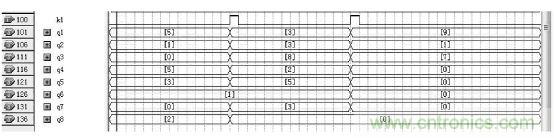

若仿真參數(shù)設(shè)置數(shù)值為:2013 年05 月15 日,星期三,15:28(33 s),定時(shí)為07:19。仿真后結(jié)果如圖4所示。

從圖4可以看出,通過K1 按鍵控制顯示,開始顯示年月日:20130515,當(dāng)按下K1 兩下,顯示星期+時(shí)間:03152833;再按兩下顯示定時(shí)時(shí)間:00000719。仿真結(jié)果與預(yù)期設(shè)計(jì)一致,設(shè)計(jì)正確。

鬧鐘模塊設(shè)計(jì)為當(dāng)定時(shí)時(shí)間到或者整點(diǎn)時(shí)鬧鈴響,分別有ZHENG,NAO 兩個(gè)控制端子控制,低電平有效。經(jīng)驗(yàn)證,定時(shí)和整點(diǎn)報(bào)時(shí)仿真結(jié)果均符合設(shè)計(jì)要求。

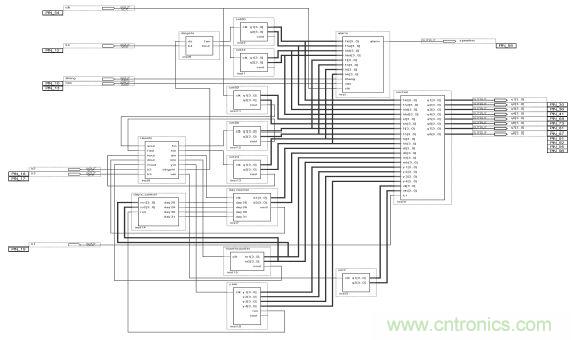

3.8 頂層模塊

將各個(gè)子模塊設(shè)計(jì)好之后,并創(chuàng)建各自文件的圖元,以供原理圖設(shè)計(jì)文件中調(diào)用。然后在原理圖編輯窗口創(chuàng)建頂層原理圖文件shuzirili.bdf,即將各圖元的引線端子按照邏輯關(guān)系連接起來,得到如圖5所示的完整原理圖,也即頂層模塊。

對(duì)頂層文件分別進(jìn)行時(shí)間、日期、鬧鈴功能的波形仿真,得到的仿真結(jié)果和預(yù)想設(shè)計(jì)一致,表明設(shè)計(jì)正確。

4 硬件驗(yàn)證

在Quartus Ⅱ開發(fā)環(huán)境中完成上述軟件設(shè)計(jì)及仿真后,最后還需將程序下載到FPGA器件中進(jìn)行硬件測(cè)試,以進(jìn)一步驗(yàn)證所設(shè)計(jì)程序是否正確。硬件驗(yàn)證時(shí),還需對(duì)頂層文件進(jìn)行管腳分配、并編譯,然后將編譯好的目標(biāo)文件通過下載電纜下載到FPGA 開發(fā)板中進(jìn)行驗(yàn)證和調(diào)試。

采用GW48-SPOC/EDA 實(shí)驗(yàn)開發(fā)系統(tǒng)并設(shè)置在工作模式0來驗(yàn)證設(shè)計(jì)結(jié)果。下面僅給出部分驗(yàn)證結(jié)果。剛完成下載,數(shù)碼管顯示20000000,按兩下K1切換到時(shí)間顯示,才剛剛開始計(jì)數(shù),同時(shí)揚(yáng)聲器發(fā)出“滴答滴答”的頻率為1 Hz的響聲(為整點(diǎn)報(bào)時(shí))60 s,然后通過按鍵8(K1)、鍵7(K2)、鍵6(K3)、鍵5(K4)對(duì)各個(gè)功能進(jìn)行驗(yàn)證。首先調(diào)整時(shí)間,按兩下K2鍵切換到分的調(diào)整,此時(shí)每按兩下K3 鍵,分鐘加1,驗(yàn)證過程中看到加到59就變?yōu)?0;再按兩下K2鍵切換到小時(shí)的調(diào)整,此時(shí)每按兩下K3鍵,分鐘加1;用同樣的方法調(diào)整星期,天,月,年以及定時(shí)的分鐘和小時(shí)。

調(diào)整日期為2013年7月31號(hào),當(dāng)再調(diào)整天時(shí),就變?yōu)?013年7月1號(hào),結(jié)果如圖9所示。其他月份實(shí)驗(yàn)結(jié)果也符合生活規(guī)律,與設(shè)計(jì)要求一致。

其他的測(cè)試結(jié)果,數(shù)碼管能夠正確顯示計(jì)時(shí)時(shí)間,定時(shí)驗(yàn)證及時(shí)間調(diào)節(jié)、整點(diǎn)報(bào)時(shí)均能夠正常工作,實(shí)驗(yàn)結(jié)果符合設(shè)計(jì)要求。

本文基于FPGA 環(huán)境設(shè)計(jì)了一個(gè)具有年、月、日、星期、時(shí)、分、秒計(jì)時(shí)顯示功能,時(shí)間調(diào)整功能和整點(diǎn)報(bào)時(shí)功能的數(shù)字日歷系統(tǒng),并將之下載到FPGA 芯片EP1C3T144-3 上進(jìn)行結(jié)果驗(yàn)證,實(shí)驗(yàn)驗(yàn)證表明:數(shù)碼管能夠正確顯示計(jì)時(shí)時(shí)間,能夠通過按鍵調(diào)整時(shí)間,能夠設(shè)定時(shí)間并調(diào)整,整點(diǎn)報(bào)時(shí)能夠正常工作,實(shí)驗(yàn)結(jié)果符合設(shè)計(jì)要求。由于設(shè)計(jì)中利用硬件描述語(yǔ)言和FPGA芯片相結(jié)合進(jìn)行數(shù)字日歷的研究,即利用EDA 技術(shù)在一定程度上實(shí)現(xiàn)了硬件設(shè)計(jì)軟件化,使設(shè)計(jì)過程變得相對(duì)簡(jiǎn)單,易于修改。

相關(guān)閱讀:

FPGA有門道?一款軟件無(wú)線電平臺(tái)的設(shè)計(jì)

利用CPLD數(shù)字邏輯和FPGA實(shí)現(xiàn)ADC

基于FPGA的航空電子系統(tǒng)的設(shè)計(jì)