【導(dǎo)讀】本文主要基于芯片測試目的,針對外圍電路中的環(huán)路濾波器設(shè)計來進(jìn)行討論,文中給出了一種簡單、易行的工程化計算方法和流程,并對其進(jìn)行了驗證測試,測試結(jié)果滿足芯片測試的需要。這種方法已經(jīng)應(yīng)用于多款小數(shù)分頻頻率合成器的測試電路的設(shè)計中。

小數(shù)分頻頻率合成器在測試時必須外接一個環(huán)路濾波器電路與壓控振蕩器才能構(gòu)成一個完整的鎖相環(huán)電路。其外圍電路中環(huán)路濾波器的設(shè)計好壞將直接影響到芯片的性能測試。以ADF4153小數(shù)分頻頻率合成器為例,研究了其外圍環(huán)路濾波器的設(shè)計方法,給出了基于芯片測試的環(huán)路濾波器設(shè)計流程,并進(jìn)行了驗證測試。

測試結(jié)果表明,該濾波器可滿足小數(shù)分頻頻率合成器芯片測試的需要。在進(jìn)行小數(shù)分頻頻率合成器的芯片測試時,數(shù)字部分可以通過常規(guī)的數(shù)字測試方法即可以實(shí)現(xiàn);而輸出射頻信號的相位噪聲、雜散噪聲則需要芯片工作在正常的輸出狀態(tài)下才能測試。小數(shù)分頻頻率合成器芯片在測試時需要與外接環(huán)路濾波器(LF)、壓控振蕩器(VCO)才能構(gòu)成完整的鎖相環(huán)回路,在具備正常的芯片功能的前提下才能實(shí)現(xiàn)對其相位噪聲、雜散噪聲下的測試。

一般而言,壓控振蕩器均使用現(xiàn)成的器件,在挑選器件時注意性能指標(biāo)的匹配就可以,只有環(huán)路濾波器才是需要計算和設(shè)計的。環(huán)路濾波器在整個電路中主要作為一個低通濾波器,它將芯片鑒相器輸出的脈沖信號進(jìn)行低通濾波,將高頻分量濾除,最終得到一個相對平滑的直流電壓信號去控制VCO工作,從而獲得一個穩(wěn)定的頻率輸出。環(huán)路濾波器的性能將直接影響到小數(shù)分頻頻率合成器芯片性能的測試。

本文以ADF 4153型小數(shù)分頻頻率合成器為例,給出了容易實(shí)現(xiàn)的三階環(huán)路濾波器的設(shè)計方法,能夠滿足芯片實(shí)際測試的需要。

外接環(huán)路濾波器的設(shè)計

環(huán)路濾波器是電荷泵鎖相環(huán)電路的重要環(huán)節(jié),它連接在電荷泵和壓控振蕩器之間。鎖相環(huán)的基本頻率特性是由環(huán)路濾波器決定的。實(shí)際上,正是由于環(huán)路濾波器的存在,鎖相環(huán)才可以選擇工作在任意的中心頻率和帶寬內(nèi)。環(huán)路濾波器的類型多種多樣,大致分為有源濾波器和無源濾波器兩大類,無源濾波器與有源濾波器相比,其優(yōu)點(diǎn)在于:結(jié)構(gòu)簡單、低噪聲、高穩(wěn)定度和易以實(shí)現(xiàn)。

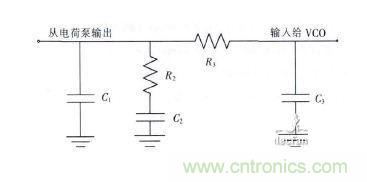

最常見的無源濾波器是如圖1所示的三階濾波器。一般而言,環(huán)路濾波器的帶寬應(yīng)為PFD頻率(通道間隔)的1/10.提高環(huán)路帶寬會縮短鎖定時間。但環(huán)路帶寬過大會大幅度地增加不穩(wěn)定性,從而導(dǎo)致鎖相環(huán)無法鎖定的狀態(tài)。

圖1三階環(huán)路濾波器

環(huán)路濾波器設(shè)計參數(shù)的選擇

為了研究環(huán)路濾波器對鎖相環(huán)輸出頻率相位噪聲的影響,設(shè)計出符合芯片測試需要的外圍環(huán)路濾波器。我們在ADIsimPLL軟件中進(jìn)行了如下仿真配置。器件型號:ADF 4153,fPFD=25MHz(理想信號源),INT=69,F(xiàn)RAC=101,MOD=125,VCO采用ZComm公司的V674ME34-LF,在該配置下,預(yù)期輸出的RFOUT=1.7452GHz.

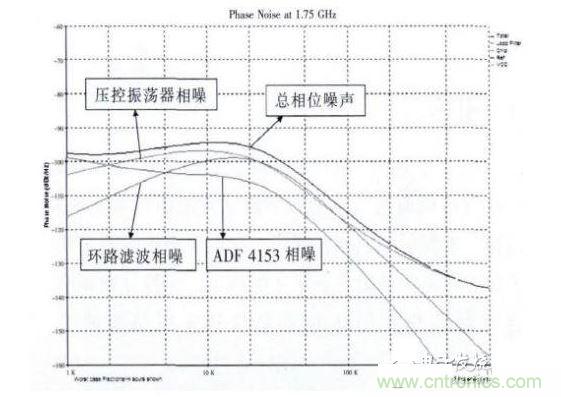

a)設(shè)定環(huán)路濾波器帶寬為20kHz,相位裕度50°,其相位噪聲的仿真情況如圖2所示。

圖2環(huán)路帶寬20kHz時的相位噪聲仿真圖

從圖2中可以得知,當(dāng)環(huán)路濾波帶寬為20kHz時,VCO所引起的相位噪聲占據(jù)了主導(dǎo)地位。芯片所引起的相位噪聲則被淹沒在總輸出噪聲之下。換句話說,當(dāng)環(huán)路帶寬較窄(如20kH)的情況下,針對鎖相環(huán)輸出信號進(jìn)行相位噪聲測試,其結(jié)果并不能真正地反映芯片輸出的相位噪聲。

[page]

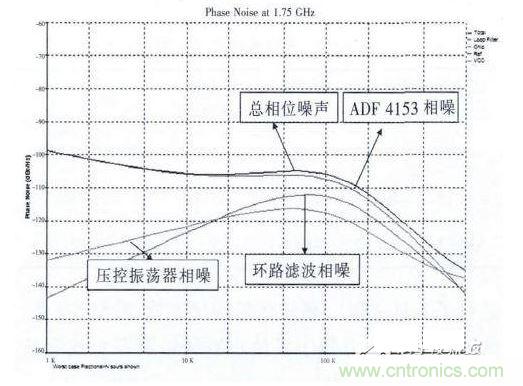

設(shè)定環(huán)路濾波器帶寬為100kHz,相位裕度50°,其相位噪聲的仿真情況如圖3所示。

圖3環(huán)路帶寬為100kHz時的相位噪聲仿真圖

從圖3中可以得知,當(dāng)環(huán)路濾波帶寬為100kHz時,VCO對于總相位噪聲的貢獻(xiàn)顯著地降低,芯片所引起的相位噪聲占據(jù)了主導(dǎo)地位,在10kHz以內(nèi),總相位噪聲輸出的曲線基本與芯片所引起的相位噪聲重合。由此可以得知,當(dāng)環(huán)路帶寬較寬(如 100kHz)的情況下,針對鎖相環(huán)輸出信號進(jìn)行相位噪聲測試,其結(jié)果基本能真正反映芯片輸出的相位噪聲。

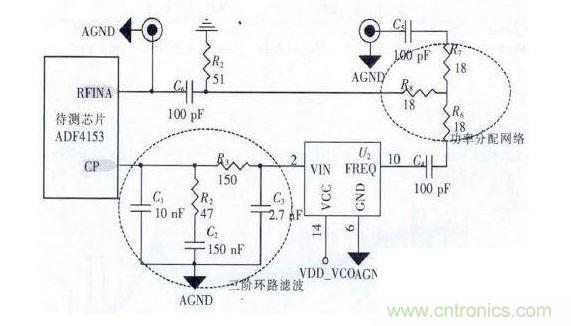

本文研究的ADF 4154的主要測試頻點(diǎn)為1.7452GHz(fPFD=25MHz,RSET=5.1k),根據(jù)測試要求進(jìn)行綜合的考慮,設(shè)定了環(huán)路帶寬75kHz,相位裕度50°的約束條件。在進(jìn)行ADF 4153的外圍電路設(shè)計時,首先需要確認(rèn)所使用的VCO型號及其標(biāo)稱性能。然后再根據(jù)ADI公司提供的ADIsim-PLL軟件進(jìn)行三階環(huán)路濾波器的設(shè)計。從軟件得出C1~C3、R2、R3的具體取值,再根據(jù)現(xiàn)有的標(biāo)稱電容電阻值進(jìn)行調(diào)整,反算出實(shí)際設(shè)計的環(huán)路帶寬及相位裕度。

由此,我們確定了環(huán)路濾波器中各個電容、電阻的取值,并設(shè)計了可用于ADF 4153芯片測試的電路原理圖,如圖4所示。VCO的輸出不僅需要連接外部頻譜儀進(jìn)行測試,還需要通過電容反饋到ADF 4153的REFINA端,同時REFINA端還需要預(yù)留SMA頭用于射頻輸入頻率范圍及靈敏度測試。一個簡單的電阻網(wǎng)絡(luò)用于完成VCO輸出信號功率的再分配。

圖4環(huán)路濾波器及射頻電路設(shè)計