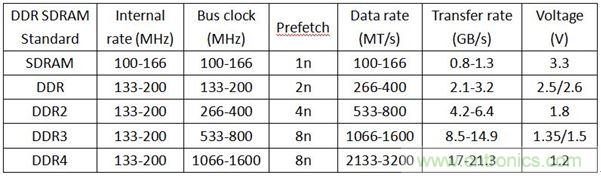

【導(dǎo)讀】在嵌入式系統(tǒng)中有各種不同種類的內(nèi)存,它們在系統(tǒng)中發(fā)揮著不可或缺的作用。但是不同種類的內(nèi)存發(fā)揮的作用也不同。本文主要講述的是DDR4,DDR3,DDR2,DDR1及SDRAM等內(nèi)存之間的相同點和不同點,及其在嵌入式系統(tǒng)中發(fā)揮的作用。

DDRSDRAM(DoubleDataRateSDRAM):為雙信道同步動態(tài)隨機存取內(nèi)存,是新一代的SDRAM技術(shù)。別于SDR(SingleDataRate)單一周期內(nèi)只能讀寫1次,DDR的雙倍數(shù)據(jù)傳輸率指的就是單一周期內(nèi)可讀取或?qū)懭?次。在核心頻率不變的情況下,傳輸效率為SDRSDRAM的2倍。第一代DDR內(nèi)存Prefetch為2bit,是SDR的2倍,運作時I/O會預(yù)取2bit的資料。舉例而言,此時DDR內(nèi)存的傳輸速率約為266~400MT/s不等,像是DDR266、DDR400都是這個時期的產(chǎn)品。

DDR2SDRAM(DoubleDataRateTwoSDRAM):為雙信道兩次同步動態(tài)隨機存取內(nèi)存。DDR2內(nèi)存Prefetch又再度提升至4bit(DDR的兩倍),DDR2的I/O頻率是DDR的2倍,也就是266、333、400MHz。舉例:核心頻率同樣有133~200MHz的顆粒,I/O頻率提升的影響下,此時的DDR2傳輸速率約為533~800MT/s不等,也就是常見的DDR2533、DDR2800等內(nèi)存規(guī)格。

DDR3SDRAM(DoubleDataRateThreeSDRAM):為雙信道三次同步動態(tài)隨機存取內(nèi)存。DDR3內(nèi)存Prefetch提升至8bit,即每次會存取8bits為一組的數(shù)據(jù)。DDR3傳輸速率介于800~1600MT/s之間。此外,DDR3的規(guī)格要求將電壓控制在1.5V,較DDR2的1.8V更為省電。DDR3也新增ASR(AutomaticSelf-Refresh)、SRT(Self-RefreshTemperature)等兩種功能,讓內(nèi)存在休眠時也能夠隨著溫度變化去控制對內(nèi)存顆粒的充電頻率,以確保系統(tǒng)數(shù)據(jù)的完整性。

DDR4SDRAM(DoubleDataRateFourthSDRAM):DDR4提供比DDR3/DDR2更低的供電電壓1.2V以及更高的帶寬,DDR4的傳輸速率目前可達2133~3200MT/s。DDR4新增了4個BankGroup數(shù)據(jù)組的設(shè)計,各個BankGroup具備獨立啟動操作讀、寫等動作特性,BankGroup數(shù)據(jù)組可套用多任務(wù)的觀念來想象,亦可解釋為DDR4在同一頻率工作周期內(nèi),至多可以處理4筆數(shù)據(jù),效率明顯好過于DDR3。另外DDR4增加了DBI(DataBusInversion)、CRC(CyclicRedundancyCheck)、CAparity等功能,讓DDR4內(nèi)存在更快速與更省電的同時亦能夠增強信號的完整性、改善數(shù)據(jù)傳輸及儲存的可靠性。

SDRAM(SynchronousDynamicRandomAccessMemory):為同步動態(tài)隨機存取內(nèi)存,前綴的Synchronous告訴 了大家這種內(nèi)存的特性,也就是同步。1996年底,SDRAM開始在系統(tǒng)中出現(xiàn),不同于早期的技術(shù),SDRAM是為了與中央處理器的計時同步化所設(shè)計,這 使得內(nèi)存控制器能夠掌握準備所要求的數(shù)據(jù)所需的準確時鐘周期,因此中央處理器從此不需要延后下一次的數(shù)據(jù)存取。舉例而言,PC66SDRAM以 66MT/s的傳輸速率運作;PC100SDRAM以100MT/s的傳輸速率運作;PC133SDRAM以133MT/s的傳輸速率運作,以此類推。

SDRAM 亦可稱為SDRSDRAM(SingleDataRateSDRAM),SingleDataRate為單倍數(shù)據(jù)傳輸率,SDRSDRAM的核心、 I/O、等效頻率皆相同,舉例而言,PC133規(guī)格的內(nèi)存,其核心、I/O、等效頻率都是133MHz。而SingleDataRate意指 SDRSDRAM在1個周期內(nèi)只能讀寫1次,若需要同時寫入與讀取,必須等到先前的指令執(zhí)行完畢,才能接著存取。

圖1