1、關于觸發器的分類

(1)、按晶體管性質分,可以分為BJT集成電路觸發器和MOS型集成電路觸發器。

(2)、按工作方式分,可分為異步工作方式和同步工作方式,異步工作方式也就是不受時鐘控制,像基本RS觸發器,同步方式就是受時鐘控制,稱為時鐘觸發器。

(3)、按結構方式分,可分為維持阻塞觸發器,延邊觸發器,主從觸發器等。

(4)、按邏輯功能分,可分為RS觸發器,JK觸發器,D觸發器,T觸發器,T''''觸發器等。

2、關于觸發器的邏輯功能

觸發器總體來說有四種功能:分別是置“0”、置“1”、保持、翻轉。前兩個不說了,就是高低電平,保持就是維持原狀態不變,翻轉就是從原狀態變為他的反狀態。

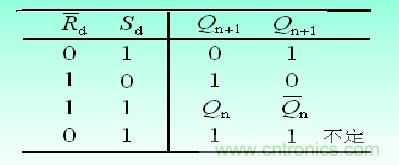

3、基本RS觸發器

這是基本RS觸發器原理圖,把兩個與非門G1、G2的輸入、輸出端交叉連接,即可構成基本RS觸發器,其邏輯電路如上圖所示。它有兩個輸入端R、S和兩個輸出端Q、Q非。

(1)、關于負脈沖和低電平

所謂負脈沖呢,就是一個信號從高電平置為低電平,然后延遲一段時間后再置為高電平的過程,就像上圖所示的脈沖。而低電平就沒有返回高電平的過程。

(2)、關于Q端

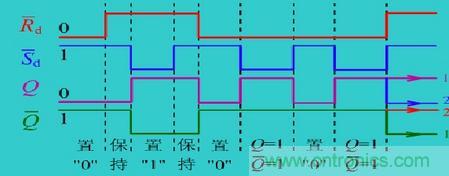

我們知道不管是置“1”端還是置“0”端,操作的都是Q端,間接操作Q非端,Rd非端和Sd非端都是控制Q端,即Sd非端一個負脈沖,Q端置“1”,Q端如果原狀態就是“1”,則加一個負脈沖后原狀態不改變。Rd非端一個負脈沖,Q端置“0”,Q端如果原狀態就是“1”,則加一個負脈沖后原狀態不改變。

(3)、兩個端口都加負脈沖的情況下

按理說兩個端口是不允許同時加負脈沖的,因為一旦兩端同時加負脈沖,則兩個輸出端就都為“1”,這樣與我們認為的兩個輸出端的值互為反變量的原則就相違背了,但是在畫時序圖的時候,可以將兩個輸出端同畫為高電平。重點是,當兩個輸入端都為低電平的時候,再把它們扳回高電平時,這時候輸出端就會有兩種結果,具體是哪種結果,這要取決于兩個門電路的運轉速度問題了。下面是RS觸發器的時序圖

下面是基本RS觸發器的真值表

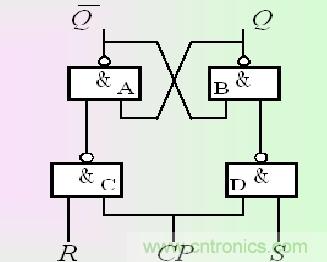

4、同步RS觸發器

同步RS觸發器是在基本RS觸發器的基礎上加了兩個與非門,CP是時鐘。

當CP為“0”時,下面兩個門電路相當于被封死,這時第一級門電路的輸出端就都為"1",即保持狀態。當CP為“1”時,門電路被打開,第一級門電路的輸出端分別為Rd非和Sd非,這就和剛才的基本RS觸發器一樣了。

[page]

5、JK觸發器

JK觸發器的內部原理相對比較復雜,對于初學者來說,直接記住他的功能就可以了,這樣不至于越學越迷糊,當然有條件的朋友也可以自己去弄明白其中的原理。

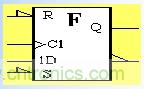

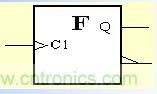

這是JK觸發器的邏輯符號,其中C1代表時鐘,左邊那個箭頭代表負脈沖有效,也就是說只有在時鐘負脈沖來臨的時候Q端才會發生變化(同步工作的情況,異步除外),R,S端為強制置“0”、“1”端,這兩個端口不受時鐘控制,可以強迫置位,R端負脈沖置“0”,S端負脈沖置“1”,J、K端為信號端。

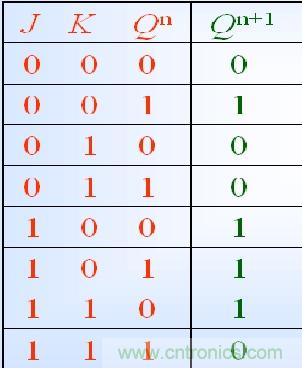

這張是JK觸發器真值表,可以看出當R、S端都為“1”的情況下,信號端的J、K才會發揮作用,從上到下依次是“保持”、置“0”、置“1”、翻轉。

這樣就可以得到JK觸發器的特性表,有了這個表,我們就可以寫出他的特性方程

![]()

即

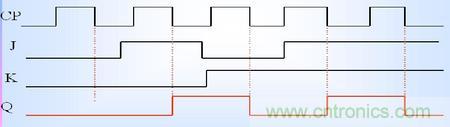

這是時序圖,注意Q端只在時鐘下降沿出變化。

6、D觸發器

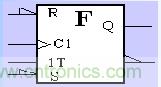

這是D觸發器的邏輯符號,注意時鐘是高電平有效,R、S端是強迫置位端,D為信號端。

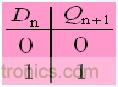

D觸發器比較簡單,真值表見下圖

[page]

7、T觸發器

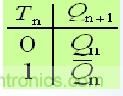

真值表

8、T’觸發器

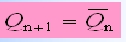

特性方程

T’觸發器的重要應用,可以用作分頻。

綜上所述,上面簡單地介紹了與FPGA有關的觸發器的分類及各觸發器的邏輯原理圖、時序圖、真值表。這些只是個人的看法與簡便的總結,希望對大家有所幫助,同時,也希望大家指出其中的不足及提出好的建議。

相關閱讀:

使用FPGA進行工業設計的五大優勢

http://www.77uud.com/gptech-art/80021010

可簡化FPGA應用設計的高速模數轉換器

http://www.77uud.com/gptech-art/80018543

實用技術:利用FPGA技術設計設計步進電機系統

http://www.77uud.com/power-art/80022131