【導讀】前面小編介紹了電容的參數ESR和ESL,以及電容并聯與串聯,本節將面對PDN目標阻抗的設計要求,我們如何選擇電容?其實目標阻抗計算也是有很多爭議性問題的,比如轉折頻率如何確定,電流隨頻率的變化如何界定與評估。

上一篇文章提出的問題是:2.5V電源,最大工作電流為5安培,手冊上要求設計電源噪聲小于5%,那么我們設計的目標阻抗是多大?很多朋友都回答正確,答案是50毫歐,大家一起加3分。其實目標阻抗計算也是有很多爭議性問題的,比如轉折頻率如何確定,電流隨頻率的變化如何界定與評估。這些問題討論起來篇幅很長,也歡迎大家移步到PCBTime的相關帖子進行交流。

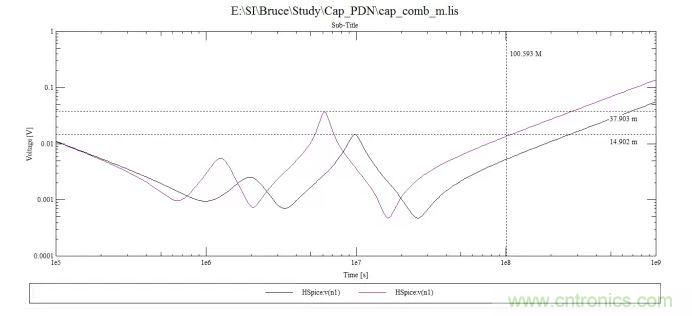

圖1是采用100uf,10uf和0.1uf電容組成的阻抗曲線。黑色曲線沒有考慮安裝電感,紫色曲線簡單評估了一下安裝電感。這是我們大部分項目采用的電容組合,能看到基本可以滿足100M以內50毫歐的目標阻抗設計要求。這也驗證了我們現在使用這樣的電容組合是符合電源設計要求的。唯一的缺點就是在部分頻段,電容的數量有點過設計。

圖1

但是隨著電壓降低,電流增大,最直接的后果就是目標阻抗減小。部分的低壓Core電源,設計目標阻抗在10毫歐以下,甚至只有幾毫歐。這時候可以有兩種方法達到這個目標。

1、繼續增加各頻段電容的數量,通過電容并聯的效果,拉低諧振頻率點的PDN阻抗,從而拉動整個阻抗曲線降低。這個做法往往事倍功半,大量的同種類電容(如0.1uf電容)起的效果并不好,對反諧振的抑制作用很小。

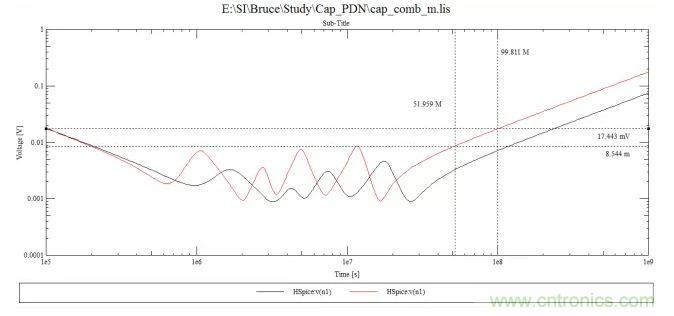

2、增加電容種類,可以用最合適的電容組合來實現PDN的設計要求。如圖2所示,沒有增加電容的總數量,只是優化了電容容值選擇,就基本實現了50M以內8毫歐的阻抗設計,100M以內的阻抗設計也比圖1要小很多。

圖2

(注:圖1和圖2采用了Hspice仿真,模擬多種電容并聯的效果,由于等效電路網表的寫法,縱坐標單位顯示是電壓V,但是取值等效于阻抗。大家如果對這個Hspice網表有興趣,可以在PCBtime論壇上進行討論交流)

(注:其他軟件,如Designer和ADS也可以實現多種電容并聯效果的仿真,電路的處理會有不同的技巧,也可以在PCBtime論壇上進行討論交流)

從以上的討論可以看出,電容取值的技巧,可以很大程度上改變PDN的阻抗曲線,從而影響到電源噪聲。如何進行電容取值,會有很多的經驗與技巧,需要在實踐中進行摸索。當然,現在也有很有很多智能式的軟件可以幫助我們進行評估,如Sigrity的Optimize PI工具,功能就非常強大。

當然,電容取值是不是滿足自阻抗的Target要求就夠了,還是需要考慮更復雜的如EMC設計需求,業內也還有一些不同的看法。

不管是同事,還是自媒體網友,大家都希望高速先生給出一些簡單實用的設計規則。在現實的世界里,設計的復雜性越來越高,簡單的規則很難保證準確性。很可能我們的文章在介紹誤區,然后我們又繼續給出一些還是“誤區”的規則。

電容選擇總結,先做一些限定,方便后面描述:

Ø 常規電源設計:在本文定義為目標阻抗要求在20毫歐以上的電源設計,普遍來說,要么就是電壓不是很低,或者電流不是非常大。

Ø 低電壓大電流的設計:在本文定義為目標阻抗要求在10毫歐以下的電源設計。

1、常規的電源設計,現在普遍采用的電容選擇方案是可行的,可以滿足電源的噪聲需求。但是電容數量過多,導致浪費,同時浪費了板上的有效布局布線空間。

2、常規的電源設計,可以通過PDN的仿真評估,或者一些芯片公司提供的電容設計Excel表格工具來進行評估,大幅減少電容的使用。

3、低電壓大電流的設計,推薦進行直流電壓跌落仿真和PDN仿真,可以有效改善電源設計質量。

4、低電壓大電流的設計,如果不做仿真,電容取值可以遵循10倍容量范圍選擇三種電容的方案,增多電容的種類,降低反諧振。