- 可測性掃描設計

- 邊界掃描技術

- 離線自測試設計

隨著集成芯片功能的增強和集成規模的不斷擴大,芯片的測試變得越來越困難,測試費用往往比設計費用還要高,測試成本已成為產品開發成本的重要組成部分,測試時間的長短也直接影響到產品上市時間進而影響經濟效益。為了使測試成本保持在合理的限度內,最有效的方法是在芯片設計時采用可測性設計(DFT)技術。可測性設計是對電路的結構進行調整,提高電路的可測性即可控制性和可觀察性。集成芯片測試之所以困難,有兩個重要原因:(1)芯片集成度高,芯片外引腳與內部晶體管比數低,使芯片的可控性和可觀察性降低;(2)芯片內部狀態復雜,對狀態的設置也非常困難。

解決芯片測試的最根本途徑是改變設計方法:在集成電路設計的初級階段就將可測性作為設計目標之一,而不是單純考慮電路功能、性能和芯片面積。實際上可測性設計就是通過增加對電路中的信號的可控性和可觀性以便及時、經濟的產生一個成功的測試程序,完成對芯片的測試工作。

可測性設計的質量可以用5個標準進行衡量:故障覆蓋率、面積消耗、性能影響、測試時間、測試費用。如何進行可行的可測性設計,使故障覆蓋率高,面積占用少,盡量少的性能影響,測試費用低,測試時間短,已成為解決集成電路測試問題的關鍵。

1掃描設計

1.1簡介

掃描設計是一種應用最為廣泛的可測性設計技術,測試時能夠獲得很高的故障覆蓋率。設計時將電路中的時序元件轉化成為可控制和可觀測的單元,這些時序元件連接成一個或多個移位寄存器(又稱掃描鏈)。這些掃描鏈可以通過控制掃描輸入來置成特定狀態,并且掃描鏈的內容可以由輸出端移出。

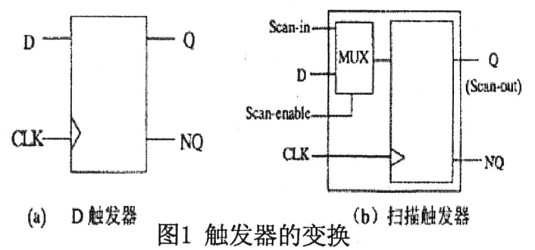

假設電路中的時序元件是由圖1(a)所示的D觸發器組成,寄存器變化法就是將此D觸發器轉化成圖1(b)所示的具有掃描功能的觸發器。從圖中可以看出掃描觸發器主要是在原觸發器的D輸入端增加了一個多路選擇器,通過掃描控制信號(Scan—enable)來選擇觸發器的輸入數據是正常工作時的輸入信號(D)還是測試掃描數據(Scan—in)。

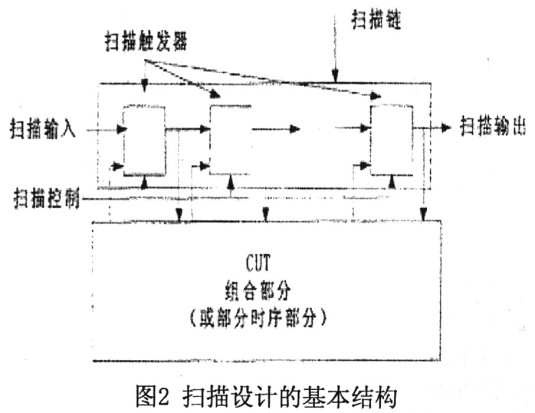

掃描設計就是利用經過變化的掃描觸發器連接成一個或多個移位寄存器,即掃描鏈。圖2為掃描設計的基本結構。這樣的設計將電路主要分成兩部分:掃描鏈與組合部分(全掃描設計)或部分時序電路(部分掃描設計),很明顯的降低了測試向量生成的復雜度。

[page]

[page]1.2掃描測試過程

在移位寄存器狀態下,第一個觸發器可以直接由初級輸入端置為特定值,最后一個觸發器可以在初級輸出直接觀察到。因此,就可以通過移位寄存器的移位功能將電路置為任意需要的初始狀態,并且移位寄存器的任一內部狀態可以移出到初級輸出端,進行觀察,即達到了可控制和可觀察的目的。此時,每一個觸發器的輸入都可以看作是一個初級輸入,輸出可以看作一個初級輸出,電路的測試生成問題就轉化成一個組合電路的測試生成問題。

電路的測試過程可以分成以下的步驟:

(1)將時序單元控制為移位寄存器狀態,即scan—en=l,并將O,1序列移入移位寄存器,然后移出,測試所有時序單元的故障;

(2)將移位寄存器置為特定的初始狀態;

(3)將所有時序單元控制為正常工作狀態,即scan一en=0,并將激勵碼加載到初級輸入端;

(4)觀察輸出端數據;

(5)向電路加時鐘脈沖信號,將新的結果數據捕獲到掃描單元中;

(6)將電路控制為移位寄存器狀態,即scan—en=l,在將移位寄存器置為下一個測試碼初態的同時,將其內容移出,轉步驟。

2邊界掃描技術

邊界掃描技術是各集成電路制造商支持和遵守的一種可測性設計標準,它在測試時不需要其它的測試設備,不僅可以測試芯片或PCB板的邏輯功能,還可以測試IC之間或PCB板之間的連接是否存在故障。邊界掃描的核心技術是掃描設計技術。

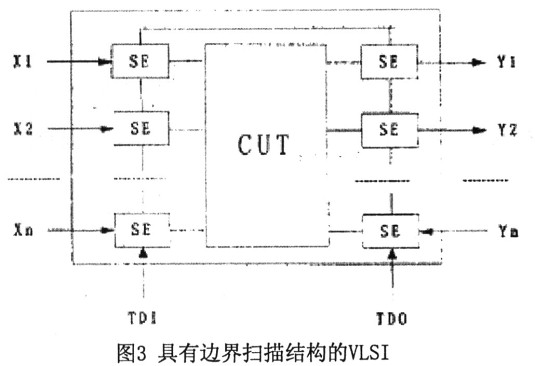

邊界掃描的基本思想是在靠近待測器件的每一個輸入/輸出管腳處增加一個邊緣掃描單元,并把這些單元連接成掃描鏈,運用掃描測試原理觀察并控制待測器件邊界的信號。在圖3中,與輸入節點X1,X2…、Xm和輸出節點Y1,Y2…、Ym連接的SE即為邊界掃描單元,它們構成一條掃描鏈(稱為邊界掃描寄存器一BSR),其輸入為TDI(TestDataInput),輸出TD0(TestData0ut)。在測試時由BSR串行地存儲和讀出測試數據。此外,還需要兩個測試控制信號:測試方式選擇(TestModeSelect—TMS)和測試時鐘(TestC1ock—TCK)來控制測試方式的選擇。

邊界掃描技術降低了對測試系統的要求,可實現多層次、全面的測試,但實現邊界掃描技術需要超出7%的附加芯片面積,同時增加了連線數目,且工作速度有所下降。

3內建自測試設計

傳統的離線測試對于日趨復雜的系統和集成度日趨提高的設計越來越不適應:一方面離線測試需要一定的專用設備;另一方面測試向量產生的時間比較長。為了減少測試生成的代價和降低測試施加的成本,出現了內建自測試技術(BIST)。BIST技術通過將外部測試功能轉移到芯片或安裝芯片的封裝上,使得人們不需要復雜、昂貴的測試設備;同時由于BIST與待測電路集成在一塊芯片上,使測試可按電路的正常工作速度、在多個層次上進行,提高了測試質量和測試速度。

內建自測試電路設計是建立在偽隨機數的產生、特征分析和掃描通路的基礎上的。采用偽隨機數發生器生成偽隨機測試輸入序列;應用特征分析器記錄被測試電路輸出序列(響應)的特征值:利用掃描通路設計,串行輸出特征值。當測試所得的特征值與被測電路的正確特征值相同時,被測電路即為無故障,反之,則有故障。被測電路的正確特征值可預先通過完好電路的實測得到,也可以通過電路的功能模擬得到。

由于偽隨機數發生器、特征分析器和掃描通路設計所涉及的硬件比較簡單,適當的設計可以共享邏輯電路,使得為測試而附加的電路比較少,容易把測試電路嵌入芯片內部,從而實現內建自測試電路設計。

本文主要介紹了可測性設計的重要性及目前所采用的一些設計方法,包括:掃描設計(scanDesign)、邊界掃描設計(BoundaryScanDesign)和內建自測試設計(BIST)。這些設計方法各有其優缺點,在實際設計時常常根據測試對象的不同,選擇不同的可測性設計方法,以利用其優點,彌補其不足。