1)使用synplify pro對(duì)硬件描述語(yǔ)言編譯并生成netlist

綜合前要注意對(duì)器件的選擇,方法是在project->implementation option中對(duì)要下載的器件和網(wǎng)表的生成情況進(jìn)行選擇。綜合后的網(wǎng)表有兩種: RTL級(jí)網(wǎng)表和門(mén)級(jí)網(wǎng)表(gate netlist),通過(guò)對(duì)網(wǎng)表的分析可以對(duì)設(shè)計(jì)的實(shí)現(xiàn)方式有初步的了解,并分析其中的錯(cuò)誤和不合理的地方,另外還可以對(duì)關(guān)鍵路徑的delay和slack進(jìn)行分析。

使用synplify pro要先新建工程,注意修改工作目錄,然后添加所要編譯的文件,要注意top文件要最后一個(gè)添加,這樣才可以保證生成的文件是以top文件來(lái)命名的

2)使用modelsim進(jìn)行功能仿真

導(dǎo)入源程序和testbench進(jìn)行仿真,并保存波形文件(.wlf)

3)使用quartusⅡ根據(jù)netlist進(jìn)行布線,并進(jìn)行時(shí)序分析

在使用quartusⅡ前要做一些必要的設(shè)置,在assignments->eda tools setting中的simulation中選擇modelsim,并選擇選項(xiàng)run this tools automatically after compilation。如果沒(méi)有提前做這些設(shè)置,可以quartus做完編譯布線后,做同樣的設(shè)置,然后運(yùn)行EDA netlist writer和eda simulation tool

在使用synplify pro得到滿意的netlist后,可以在synplify pro中通過(guò)option-> quartusⅡ直接調(diào)用quartusⅡ,quartusⅡ?qū)ynplify pro生成的.vqm文件進(jìn)行編譯,布線。然后根據(jù)設(shè)計(jì)要求進(jìn)行時(shí)序分析和引腳調(diào)整。

4)使用modelsim進(jìn)行布線后仿真

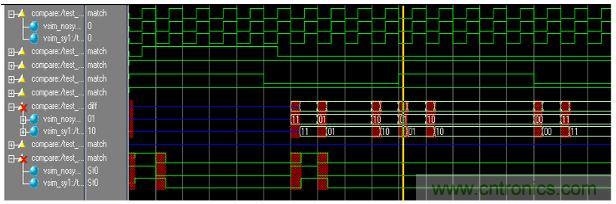

由于quartusⅡ提前做了設(shè)置,因此在編譯布線完成后,會(huì)在工作目錄下生成modelsim仿真所需要的文件和庫(kù)(modelsim_work),在modelsim中將產(chǎn)生的文件和庫(kù)所在的文件夾設(shè)置為當(dāng)前目錄,modelsim_work庫(kù)會(huì)自動(dòng)導(dǎo)入,新建工程會(huì)提示所使用的modelsim.ini文件,應(yīng)使用quartus生成的,然后導(dǎo)入文件(包括testbench),進(jìn)行編譯,仿真的時(shí)候在library中添加modelsim_work庫(kù),在sdf選項(xiàng)中可以添加quartus生成的延遲信息文件.sdo,注意作用域的選擇,如果testbench中調(diào)用被測(cè)試模塊的語(yǔ)句是send3a tb,那么作用域應(yīng)該寫(xiě)tb,在option選擇中可以選擇是否看代碼覆蓋率。另外,還可以將布線后的仿真結(jié)果與功能仿真的結(jié)果進(jìn)行對(duì)比。下圖就是小型Soc中send3a模塊前后仿真的對(duì)比圖

圖1

5)將quartus的波形轉(zhuǎn)化成testbench的方法:

畫(huà)好波形后,通過(guò)file->export可以將波形輸出到quatus的工作目錄,verilog語(yǔ)言擴(kuò)展名為.vt,修改為.v后可以在modelsim中使用,需要說(shuō)明的是如果波形中包括輸出端口的話,輸出的testbench包含三個(gè)模塊,一般情況下,只需將輸入波形畫(huà)好后,輸出到testbench

實(shí)際上,我們可以看出,整個(gè)過(guò)程實(shí)際就是: 代碼編寫(xiě)--->功能仿真---->綜合---->布局,布線---->門(mén)級(jí)仿真----->下載------>板子調(diào)試

這樣一看,原來(lái)HDL設(shè)計(jì)流程其實(shí)也很明了和簡(jiǎn)單..不是嗎??

相關(guān)閱讀:

工程師入門(mén)首選:FPGA學(xué)習(xí)中必須注意的要點(diǎn)

網(wǎng)友探討:FPGA電源設(shè)計(jì)適合并行工程嗎?

專(zhuān)家支招:如何為FPGA工程師節(jié)省十倍開(kāi)發(fā)時(shí)間