【導讀】深度學習在這十年,甚至是未來幾十年內都有可能是最熱門的話題。雖然深度學習已是廣為人知了,但它并不僅僅包含數學、建模、學習和優化。算法必須在優化后的硬件上運行,因為學習成千上萬的數據可能需要長達幾周的時間。因此,深度學習網絡亟需更快、更高效的硬件。

眾所周知,并非所有進程都能在CPU上高效運行。游戲和視頻處理需要專門的硬件——圖形處理器(GPU),信號處理則需要像數字信號處理器(DSP)等其它獨立的架構。人們一直在設計用于學習(learning)的專用硬件,例如,2016年3月與李世石對陣的AlphaGo計算機使用了由1920個CPU和280個GPU組成的分布式計算模塊。而隨著英偉達發布新一代的Pascal GPU,人們也開始對深度學習的軟件和硬件有了同等的關注。接下來,讓我們重點來看深度學習的硬件架構。

對深度學習硬件平臺的要求

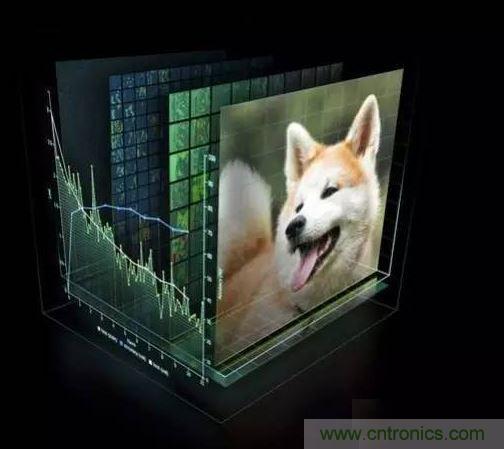

要想明白我們需要怎樣的硬件,必須了解深度學習的工作原理。首先在表層上,我們有一個巨大的數據集,并選定了一種深度學習模型。每個模型都有一些內部參數需要調整,以便學習數據。而這種參數調整實際上可以歸結為優化問題,在調整這些參數時,就相當于在優化特定的約束條件。

矩陣相乘(Matrix MulTIplicaTIon)——幾乎所有的深度學習模型都包含這一運算,它的計算十分密集。

卷積(ConvoluTIon)——這是另一個常用的運算,占用了模型中大部分的每秒浮點運算(浮點/秒)。

循環層(Recurrent Layers )——模型中的反饋層,并且基本上是前兩個運算的組合。

All Reduce——這是一個在優化前對學習到的參數進行傳遞或解析的運算序列。在跨硬件分布的深度學習網絡上執行同步優化時(如AlphaGo的例子),這一操作尤其有效。

除此之外,深度學習的硬件加速器需要具備數據級別和流程化的并行性、多線程和高內存帶寬等特性。 另外,由于數據的訓練時間很長,所以硬件架構必須低功耗。 因此,效能功耗比(Performance per Watt)是硬件架構的評估標準之一。

當前趨勢與未來走向

英偉達以其大規模的并行GPU和專用GPU編程框架CUDA主導著當前的深度學習市場。但是越來越多的公司開發出了用于深度學習的加速硬件,比如谷歌的張量處理單元(TPU/Tensor Processing Unit)、英特爾的Xeon Phi Knight‘s Landing,以及高通的神經網絡處理器(NNU/Neural Network Processor)。像Teradeep這樣的公司現在開始使用FPGA(現場可編程門陣列),因為它們的能效比GPU的高出10倍。 FPGA更靈活、可擴展、并且效能功耗比更高。 但是對FPGA編程需要特定的硬件知識,因此近來也有對軟件層面的FPGA編程模型的開發。

此外,一直以來廣為人所接受的理念是,適合所有模型的統一架構是不存在的,因為不同的模型需要不同的硬件處理架構。 而研究人員正在努力,希望FPGA的廣泛使用能夠推翻這一說法。

大多數深度學習軟件框架(如TensorFlow、Torch、Theano、CNTK)是開源的,而Facebook最近也開放其 Big Sur 深度學習硬件平臺,因此在不久的將來,我們應該會看到更多深度學習的開源硬件架構 。