【導讀】為了解電源域和電源的增長情況,我們需要追溯ADC的歷史脈絡。早在ADC不過爾爾的時候,采樣速度很慢,大約在數十MHz內,而數字內容很少,幾乎不存在。電路的數字部分主要涉及如何將數據傳輸到數字接收邏輯——專用集成電路 (ASIC) 或現場可編程門陣列 (FPGA)。用于制造這些電路的工藝節點幾何尺寸較大,約在180 nm或更大。

問:高速 ADC 為什么有如此多電源域?

答:在采樣速率和可用帶寬方面,當今的射頻模數轉換器(RF ADC)已有長足的發展。其中還納入了大量數字處理功能,電源方面的復雜性也有提高。那么,當今的RF ADC為什么有如此多不同的電源軌和電源域?

為了解電源域和電源的增長情況,我們需要追溯ADC的歷史脈絡。早在ADC不過爾爾的時候,采樣速度很慢,大約在數十MHz內,而數字內容很少,幾乎不存在。電路的數字部分主要涉及如何將數據傳輸到數字接收邏輯——專用集成電路 (ASIC) 或現場可編程門陣列 (FPGA)。用于制造這些電路的工藝節點幾何尺寸較大,約在180 nm或更大。使用單電壓軌(1.8 V )和兩個不同的域(AVDD和DVDD,分別用于模擬域和數字域),便可獲得足夠好的性能。

隨著硅處理技術的改進,晶體管的幾何尺寸不斷減小,意味著每 mm2面積上可以容納更多的晶體管(即特征)。但是,人們仍然希望 ADC 實現與其前一代器件相同(或更好)的性能。

現在,ADC 的設計采取了多層面方法,其中:

采樣速度和模擬帶寬必須得到改善;

性能必須與前一代相同或更好;

納入更多片內數字處理功能來輔助數字接收邏輯。

下面將進一步討論上述各方面特性以及它們對芯片設計構成怎樣的挑戰。

需要高速度

在 CMOS 技術中,提高速度(帶寬)的最普遍方法是讓晶體管幾何尺寸變小。使用更精細的 CMOS 晶體管可降低寄生效應,從而有助于提高晶體管的速度。晶體管速度越快,則帶寬越寬。數字電路的功耗與開關速度有直接關系,與電源電壓則是平方關系,如下式所示:

其中:

P為功耗

CLD 為負載電容

V 為電源電壓

fSW 為開關頻率

幾何尺寸越小,電路設計人員能實現的電路速度就越快,而每MHz每個晶體管的功耗與上一代相同。以 AD9680 和 AD9695為例,二者分別采用65 nm和28 nm CMOS技術設計而成。在1.25 GSPS和1.3GSPS時,AD9680和AD9695的功耗分別為3.7 W和1.6 W。這表明,架構大致相同時,采用28 nm工藝制造的電路功耗比采用65 nm工藝制造的相同電路的功耗要低一半。因此,在消耗相同功率的情況下,28 nm工藝電路的運行速度可以是65 nm工藝電路的一倍。AD9208很好地說明了這一點。

裕量最重要

對更寬采樣帶寬的需求促使業界采用更精細的幾何尺寸,不過對數據轉換器性能(如噪聲和線性度)的期望仍然存在。這對模擬設計提出了獨特的挑戰。轉向更小幾何尺寸的一個不希望出現的結果是電源電壓降低,這使得開發模擬電路以工作在高采樣速率并保持相同的噪聲/線性度性能所需的裕量大大降低。為了克服這一限制,電路設計有不同的電壓軌以提供所需的噪聲和線性度性能。

例如在 AD9208中,0.975 V電源為需要快速切換的電路供電。這包括比較器和其他相關電路,以及數字和驅動器輸出。1.9 V電源為基準電壓和其他偏置電路供電。2.5 V電源為輸入緩沖器供電,而要在高模擬頻率下工作,裕量必須很高。沒有必要為緩沖器提供2.5 V電源,它也可以工作在1.9 V。電壓軌的降低會導致線性度性能下降。

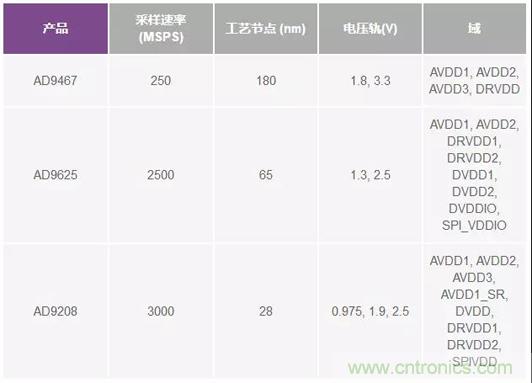

數字電路不需要裕量,因為最重要的參數是速度。所以,數字電路通常以最低電源電壓運行,以獲取CMOS開關速度和功耗的優勢。這在新一代ADC中很明顯,最低電壓軌已降低至0.975 V。下面的表1列出了若干代的一些常見ADC。

表1:產品比較

隔離是關鍵

隨著業界轉向深亞微米技術和高速開關電路,功能集成度也在提高。以 AD9467 和A D9208為例,AD9467采用180 nm BiCMOS工藝,而AD9208采用28 nm CMOS工藝。當然,AD9467的噪聲密度約為-157 dBF S/Hz,而AD9208的噪聲密度約為-152 dBF S/Hz。 但是,如果拿數據手冊做一個簡單的計算,取總功耗(每通道)并將其除以分辨率和采樣速率,就可以看到A D9467的功耗約為330μW/位/MSPS,而AD9208僅為40μW/位/MSPS。

與AD9467相比,AD9208具有更高的采樣速率(3 GSPS對250 MSPS)和高得多的輸入帶寬(9 GHz對0.9 GHz),并且集成了更多數字特性。A D9208可以完成所有這些工作,每位每MSPS的功耗只有大約1/8。每位每MSPS的功耗不是工業標準指標,其在本例中的作用是突出ADC設計中使用更小尺寸工藝的好處。當超快電路在非常近的距離內運行時,各個模塊之間總會存在耦合或震顫的風險。

為了改善隔離,設計者必須考慮各種耦合機制。最明顯的機制是通過共享電源域。如果電源域盡可能遠離電路,那么共享同一電壓軌(AD9208為0.975 V)的數字電路和模擬電路發生震顫的可能性將非常小。在硅片中,電源已被分開,接地也是如此。封裝設計繼續貫徹了這種隔離電源域處理。由此所得的同一封裝內不同電源域和地的劃分,如表2所示,其以AD9208為例。

表2:AD9208電源域和接地域

顯示AD9208各不同域的引腳排列圖如圖1所示。

圖1. AD9208引腳配置(頂視圖)

這可能會讓系統設計人員驚慌失措。乍一看,數據手冊給人的印象是這些域需要分開處理以優化系統性能。

看不到盡頭?

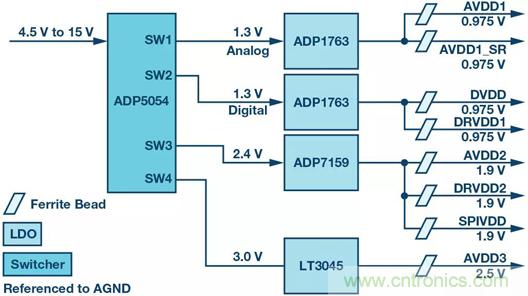

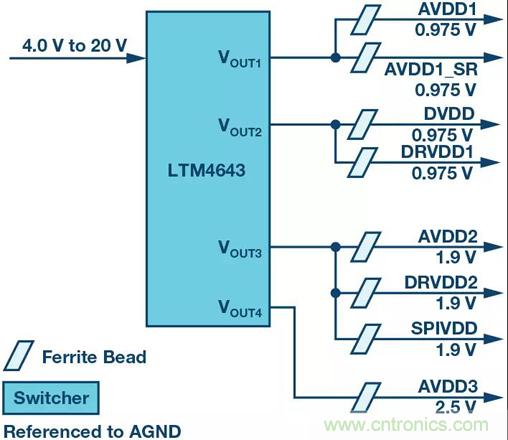

情況并不像看起來那么可怕。數據手冊的目的僅僅是喚起人們對各種敏感域的關注,讓系統設計人員可以關注PDN(電源輸送網絡)設計,對其進行適當的劃分。共享相同供電軌的大多數電源域和接地域可以合并,因此PDN可以簡化。這導致BOM(物料清單)和布局得以簡化。根據設計約束,圖2和圖3顯示了AD9208的兩種PDN設計方法。

圖2. AD9208引腳配置(頂視圖)

圖3. AD9208 PDN,DC-DC轉換器為所有域供電

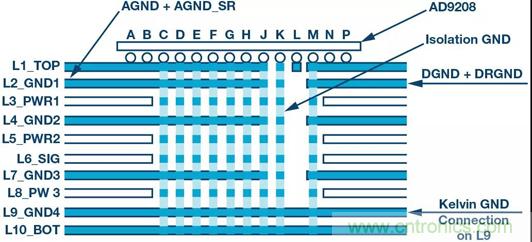

通過充分濾波和布局分離,各個域可以合理布置,使得ADC性能最大化,同時降低BOM和PDN復雜性。各接地域采用開爾文連接方法也會改善隔離。從網表角度來看,仍然只有一個GND網。電路板可以劃分為不同接地域以提供充分的隔離。在AD9208的評估板AD9208-3000EBZ中,不同接地分區在第9層上形成開爾文連接。圖4所示為10層PCB(印刷電路板)AD9208-3000EBZ的橫截面,其顯示了不同GND連接。

圖4. AD9208下方的AD9208-3000 EBZ PCB橫截面

所以,這不是世界末日?

絕對不是。僅僅因為AD9208數據手冊顯示了所有這些域,并不意味著它們在系統板上必須全部分離。了解系統性能目標和ADC目標性能對優化ADC的PDN起著重要作用。在電路板上使用智能分區以減少不必要的接地回路,是將各個域之間的串擾降到最低的關鍵。適當地共享電源域,同時滿足隔離要求,將能簡化PDN和BOM。

推薦閱讀: