【導讀】前面有講到設計人員因為沒有留意到DDR3主控沒有讀寫平衡功能,就按照常規的布線要求來走線,導致數據和時鐘信號長度差異較大,最終使得DDR3系統運行不到額定頻率。看來沒有讀寫平衡的DDR3,直接按照DDR2的設計規則來做還是比較靠譜的,那么DDR2的設計到底有哪些規則呢?我想大家肯定會比較感興趣吧。

到底有哪些規則呢?所謂實踐出真理,還是先來看看下面的這個案例吧!

這個DDR2系統采用8片顆粒表底貼的設計,地址、控制、命令信號一拖八,其余信號一拖二,但最終的系統跑不起來。查看PCB設計,列出部分信號的截圖如下,先不評論,各位慢慢開始來找茬吧。

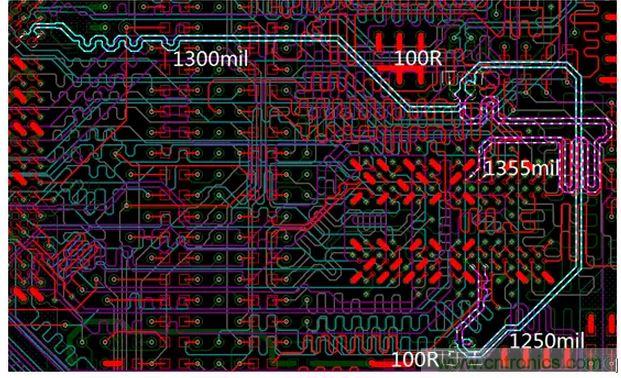

上圖高亮部分為時鐘信號(綠白)的走線,從主控芯片出來換層經過1300mil到分支過孔,此處端接一個100ohm差分阻抗,再從過孔處分支各走一段1250mil和1350mil的走線到表底兩個顆粒,其中一個顆粒再端接一個100歐姆差分電阻,其他的時鐘信號也大致如此。

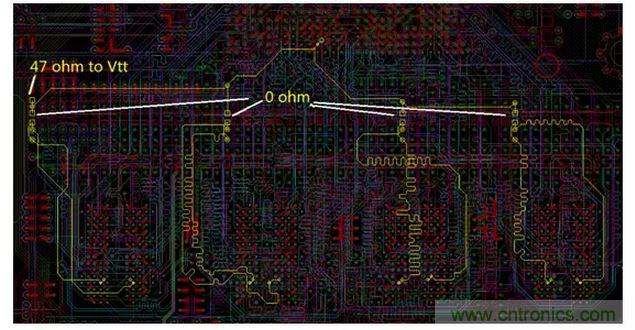

圖中黃色高亮部分為地址信號走線,從主控芯片出來馬上第一級分支,再約600mil進行第二級分支,再一個分支經過1000mil進行第三級分支,另一分支在50mil左右也開始第三級分支,最后接0ohm串阻約1100mil到顆粒,其中在最邊上某一第三分支過孔處上拉一個47ohm電阻到Vtt,其他的地址、控制信號也大致如此結構。

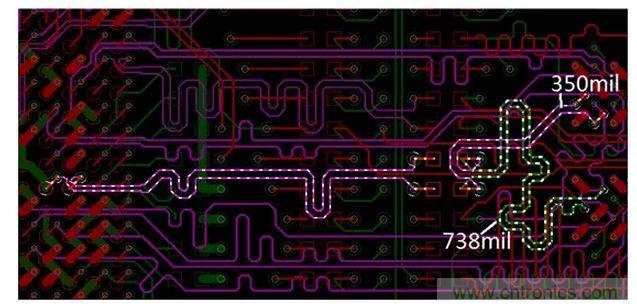

再來看DQS信號,如上圖高亮玫紅白點信號,進過一級分支各0ohm串阻經350mil和738mil的線路到表底層顆粒,其他的差異不大。

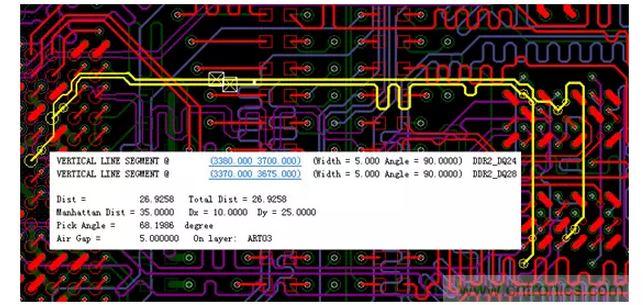

最后再看數據信號,圖中黃色高亮部分,采用的菊花鏈結構,先到其中一個顆粒,再到另一面的第二個顆粒,其他的數據信號也是這種結構。

好了,其他的如電源我們就不用看了,看到這里我們已經大致知道這個DDR2系統跑不起來是有原因的啦。