【導(dǎo)讀】可編程邏輯器件在數(shù)字系統(tǒng)的發(fā)展史中可以說是最亮的一筆。PLD能夠完成任何數(shù)字器件的功能,用PLD來開發(fā)數(shù)字電路能夠減少PCB面積,提高系統(tǒng)的可靠性,而且還大大減少了設(shè)計(jì)時間。由PLD延伸出的FPGA和CPLD都是可編程邏輯器件。

1 PLD發(fā)展過程

早期的可編程邏輯器件只有可編程只讀存貯器(PROM)、紫外線可擦除只讀存貯器(EPROM)和電可擦除只讀存貯器(E2PROM)三種。由于結(jié)構(gòu)的限制,他們只能完成簡單的數(shù)字邏輯功能。

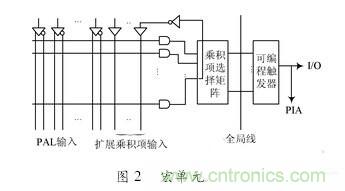

稍后,出現(xiàn)了一類結(jié)構(gòu)上稍復(fù)雜的可編程芯片,即可編程邏輯器件(PLD),他能夠完成各種數(shù)字邏輯功能。這一階段(大約20世紀(jì)70年代中期)的產(chǎn)品主要有可編程陣列邏輯(ProgrammableArrayLogic,PAL),PAL由一個可編程的“與”平面和一個固定的“或”平面構(gòu)成,或門的輸出可以通過觸發(fā)器有選擇地被置為寄存狀態(tài)。PAL器件是現(xiàn)場可編程的,他的實(shí)現(xiàn)工藝有反熔絲技術(shù)、EPROM技術(shù)和E2PROM技術(shù)。

20世紀(jì)80年代初期,在PAL的基礎(chǔ)上,又發(fā)展了一種通用陣列邏輯(GenericArrayLogic,GAL),他采用E2PROM工藝,實(shí)現(xiàn)了電可按除、電可改寫,其輸出結(jié)構(gòu)是可編程的邏輯宏單元,因而他的設(shè)計(jì)具有很強(qiáng)的靈活性,至今仍有許多人使用。

20世紀(jì)80年代中期,為了彌補(bǔ)上述缺陷,又先后推出了可擦除、可編程的邏輯器件(ErasableProgrammableLogicDevice,EPLD)。CPLD和FPGA,EPLD的集成度更高,設(shè)計(jì)更靈活,但內(nèi)部連線功能較弱。

2 結(jié)構(gòu)比較

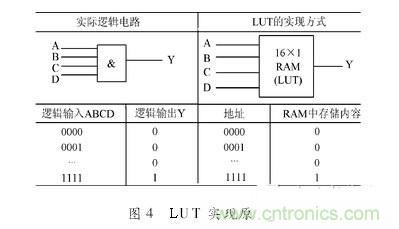

不同廠家對PLD的叫法不盡相同,但一般來說,把基于乘積項(xiàng)技術(shù),F(xiàn)LASH(類似E2PROM工藝)工藝的PLD叫CPLD;把基于查找表技術(shù),SRAM工藝,要外掛配置E2PROM的PLD叫FPGA。下面從內(nèi)部結(jié)構(gòu)對2者進(jìn)行比較。

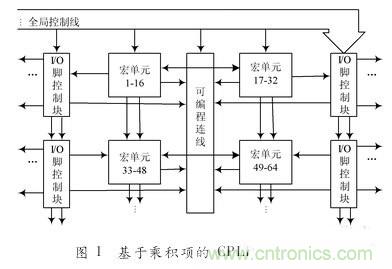

以altera的MAX7000為例,其他型號的結(jié)構(gòu)與此都非常相似,這種PLD結(jié)構(gòu)可分為3塊:宏單元(marocell),可編程連線陣列(ProgrammableInterconnectArray,PIA)和輸入輸出I/O控制塊。宏單元是CPLD的基本結(jié)構(gòu),由他來實(shí)現(xiàn)基本的邏輯功能。

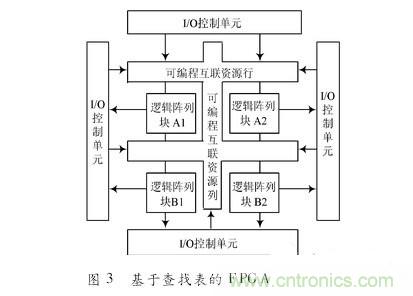

2.2 基于查找表的FPGA結(jié)構(gòu)

以Altera的FLEX/ACEX為例,這種PLD結(jié)構(gòu)主要包括邏輯陣列塊(LogicArrayBlock,LAB),輸入輸出塊(InputOutputElement,I/OE),隨機(jī)存儲器塊(RandomAccessMemory,RAM未表示出)和可編程行/列連線。其中一個LAB包括8個邏輯單元(LogicElement,LE),每個LE包括一個LUT一個觸發(fā)器和相關(guān)的相關(guān)邏輯。LE是FLEX/ACEX芯片實(shí)現(xiàn)邏輯的最基本結(jié)構(gòu)。如圖3所示。

3 功能比較

盡管CPLD和FPGA都是PLD器件,有很多共同特點(diǎn),但由于上節(jié)對CPLD和FPGA進(jìn)行結(jié)構(gòu)上比較的不同,在使用過程中仍然具有很大的差異。

一般認(rèn)為CPLD是“邏輯豐富”型的,更適合完成各種算法和組合邏輯,F(xiàn)PGA是“時序豐富”型的,更適合于完成時序邏輯。換句話說,CPLD更適合于觸發(fā)器有限而乘積項(xiàng)豐富的結(jié)構(gòu),而FPGA更適合于觸發(fā)器豐富的結(jié)構(gòu)。

(2)運(yùn)行速度

一般認(rèn)為CPLD是“邏輯豐富”型的,更適合完成各種算法和組合邏輯,F(xiàn)PGA是“時序豐富”型的,更適合于完成時序邏輯。換句話說,CPLD更適合于觸發(fā)器有限而乘積項(xiàng)豐富的結(jié)構(gòu),而FPGA更適合于觸發(fā)器豐富的結(jié)構(gòu)。

(3)編程方式

目前的CPLD主要是基于E2PROM或FLASH存儲器編程, 編程次數(shù)達(dá)1萬次;FPGA大部分是基于SRAM編程其優(yōu)點(diǎn)是可進(jìn)行任意次數(shù)的編程,并可在工作中快速編程,實(shí)現(xiàn)板級和系統(tǒng)級的動態(tài)配置,因此可稱為可重配置硬件。

4 CPLD/FPGA發(fā)展趨勢

PLD在近20年的時間里已經(jīng)得到了巨大的發(fā)展,在未來的發(fā)展中,將呈現(xiàn)以下幾個方面的趨勢:

(1) 向大規(guī)模、高集成度方向進(jìn)一步發(fā)展

當(dāng)前,PLD的規(guī)模已經(jīng)達(dá)到了百萬門級,在工藝上,芯片的最小線寬達(dá)到了0.13um,并且還會向著大規(guī)模、高集成度方向進(jìn)一步發(fā)展。

(2) 向低電壓、低功耗的方向發(fā)展

PLD的內(nèi)核電壓在不斷的降低,經(jīng)歷5V→3.3V→.5V→1.8V的演變,未來將會更低。工作電壓的降低使得芯片的功耗也大大減少,這樣就適應(yīng)了一些低功耗場合的應(yīng)用,比如移動通信設(shè)備、個人數(shù)字助理等。

(3) 向高速可預(yù)測延時方向發(fā)展

由于在一些高速處理的系統(tǒng)中,數(shù)據(jù)處理量的激增要求數(shù)字系統(tǒng)有大的數(shù)據(jù)吞吐速率,比如對圖像信號的處理,這樣就對PLD的速度指標(biāo)提出了更高的要求;另外,為了保證高速系統(tǒng)的穩(wěn)定性,延時也是十分重要的。用戶在進(jìn)行系統(tǒng)重構(gòu)的同時,擔(dān)心的是延時特性會不會因重新布線的改變而改變,如果改變,將會導(dǎo)致系統(tǒng)性能的不穩(wěn)定性,這對龐大而高速的系統(tǒng)而言將是不可想象的,帶來的損失也是巨大的。因此,為了適應(yīng)未來復(fù)雜高速電子系統(tǒng)的要求,PLD的高速可預(yù)測延時也是一個發(fā)展趨勢。

(4) 向數(shù)摸混合可編程方向發(fā)展

迄今為止,PLD的開發(fā)與應(yīng)用的大部分工作都集中在數(shù)字邏輯電路上,在未來幾年里,這一局面將會有所改變,模擬電路和數(shù)摸混合電路的可編程技術(shù)得到發(fā)展。目前的技術(shù)ISPPAC可實(shí)現(xiàn)3種功能:信號調(diào)整、信號處理和信號轉(zhuǎn)換。信號調(diào)整主要是對信號進(jìn)行放大、衰減和濾波;信號處理是對信號進(jìn)行求和、求差和積分運(yùn)算;信號轉(zhuǎn)換則是指把數(shù)字信號轉(zhuǎn)換成模擬信號。EPAC芯片集中了各種模擬功能電路,如可編程增益放大器、可編程比較器、多路復(fù)用器、可編程A/D轉(zhuǎn)換器、濾波器和跟蹤保持放大器等。

(5) 向多功能、嵌入式模塊方向發(fā)展

現(xiàn)在,PLD內(nèi)已經(jīng)廣泛嵌入RAM/ROM,F(xiàn)IFO等存儲器模塊,這些嵌入式模塊可以實(shí)現(xiàn)更快的無延時的運(yùn)算與操作。特別是美國Altrea公司于2000年對可編程片上系統(tǒng)(SystemOnProgrammableChip,SOPC)的提出,使得以FPGA為物理載體、在單一的FPGA中實(shí)現(xiàn)包括嵌入式處理器系統(tǒng)、接口系統(tǒng)、硬件協(xié)處理器或加速器系統(tǒng)、DSP系統(tǒng)、數(shù)字通信系統(tǒng)、存儲電路以及普通數(shù)字系統(tǒng)更是成為目前電子技術(shù)中的研究熱點(diǎn)。

相關(guān)閱讀:

如何實(shí)現(xiàn)高效并行的實(shí)時上采樣?FPGA獻(xiàn)計(jì)

菜鳥升級必備:通透了解FPGA設(shè)計(jì)流程

工程師入門首選:FPGA學(xué)習(xí)中必須注意的要點(diǎn)